您所在的位置:首页 - 教育 - 正文教育

消息称三星电子正研发先进封装技术,目标年二季度量产

![]() admin

08-08

【教育】

607人已围观

admin

08-08

【教育】

607人已围观

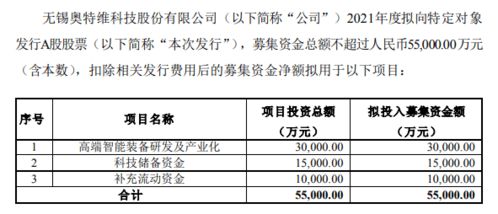

摘要7月3日消息,韩媒ETNews近日报道称,三星电子AVP先进封装部门正在开发面向AI半导体芯片的新型“3.3D”先进封装技术,目标2026年二季度实现量产。韩媒给出的概念图显示,这一3.3D封装技术整合了三星电子多项先进异构集成技术。▲图源ETNews概念图中GPU(AI计算芯片)垂直堆叠在LCC(IT之家注:即SRAM缓存)之上,两部分键合为一体,这点类似于三星电子现有X-Cube3DIC封装技术。▲三星X-Cube封装技术而在GPULCC缓存整体与HBM内存的互联中,这一3.3D封装技术又

7月3日消息,韩媒ETNews近日报道称,三星电子AVP先进封装部门正在开发面向AI半导体芯片的新型“3.3D”先进封装技术,目标2026年二季度实现量产。

韩媒给出的概念图显示,这一3.3D封装技术整合了三星电子多项先进异构集成技术。

▲图源ETNews

概念图中GPU(AI计算芯片)垂直堆叠在LCC(IT之家注:即SRAM缓存)之上,两部分键合为一体,这点类似于三星电子现有X-Cube3DIC封装技术。

▲三星X-Cube封装技术

而在GPU LCC缓存整体与HBM内存的互联中,这一3.3D封装技术又与I-CubeE2.5封装技术有不少相似之处:

▲三星I-CubeE封装技术

GPU LCC缓存整体和HBM位于铜RDL重布线中介层上,用硅桥芯片实现裸晶之间的直接连接,消息称三星电子正研发先进封装技术,目标年二季度量产而铜RDL重布线层又位于载板上方。

这一设计在大部分位置采用铜RDL重布线层代替价格可达前者十倍的硅中介层,仅在必要部分引入硅桥。

接近三星电子的消息源指出,该设计可在不牺牲芯片表现的前提下较完全采用硅中介层的方案降低22%生产成本。

此外三星电子还将在这一3.3D封装技术中引入面板级(PLP)封装,用大型方形载板替代面积有限的圆形晶圆,进一步提升封装生产效率。

韩媒认为,三星电子目标打造在价格和生产效率上均有显著优势的新一代3.3D封装技术,在目前由台积电主导的先进封装代工市场啃下更多无厂设计企业的订单。

【来源:IT之家】

Tags: 消息称三星电子正研发先进封装技术目标年二季度量产

上一篇: 我国科研人员发现一种沙漠苔藓,或可在火星环境中存活

下一篇: 宫颈糜烂会癌变吗如何预防宫颈糜烂癌变